## **Dedicated FIB Preparation for TEM Cross-section Samples of Nanowires grown vertically on Silicon Substrates**

M. Kaiser, M.A. Verheijen, A.L. Roest, E.P.A.M. Bakkers

Philips Research Laboratories, High Tech Campus 11, 5656 AE Eindhoven, The Netherlands

Higher operation speeds in silicon devices have been achieved by reducing the device dimensions. To make substantial progress, however, effort has been put in investigation of semiconductor materials that intrinsically have a higher mobility, such as GaAs, InP, and InAs. Nowadays, silicon is the standard for the electronics industry. A solution is to combine the best parts of these different technologies; i.e. the epitaxial integration of the III-V semiconductors into the mature silicon technology. This implies that the crystal lattice continues from the silicon substrate into the III-V material (e.g. nanowires). The crystalline quality of the interface between substrate and III-V material is of great importance, since it will determine the device performance. To avoid lattice defects and strain caused by the lattice mismatch the lateral dimensions of the III-V crystals have to be reduced by making vertical devices; in other words that is to grow III-V nanowires vertically on silicon [1]. Optimization of the nanowire growth process includes both electrical characterization as well as detailed structural studies by electron microscopy. Transmission Electron Microscopy (TEM) enables atomic resolution studies of this interface. However, to be able to image the interface at atomic scale, a cross section of the sample that is transparent for electrons has to be prepared. A high-end preparation method was developed to analyze selected nanowires in crosssection, for studies parallel to their growth direction, by means of Focused Ion Beam (FIB) sputtering.

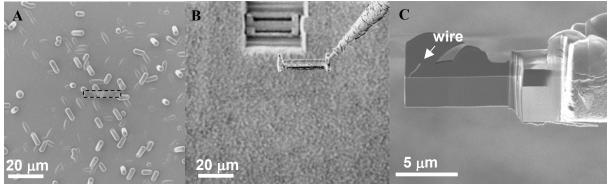

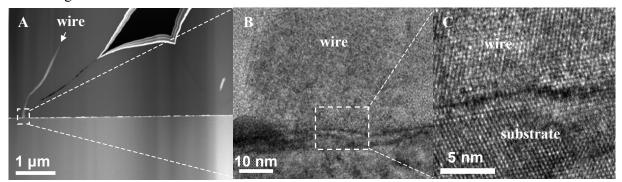

After completion of the Metallo-Organic Chemical Vapor Deposition (MOCVD) growth process [1], the nanowires are mechanically fixed by depositing a 50 nm SiO<sub>2</sub> layer on top by plasmaenhanced chemical vapor deposition. The 50 nm SiO<sub>2</sub>-layer also protects the wires during the FIB preparation. The so-called *in-situ* lift-out method [2] is used to prepare a TEM sample (see fig. 1A and B). This method enables 1) to select the nanowire of interest on forehand in the FIB and 2) to thin the sample further after TEM-inspection. The latter option is necessary since the limited thickness of the nanowires (50 nm) requires careful preparation. Lateral straggling of the Ga ions during FIB milling causes the outer 10-20 nm of the TEM sample to become heavily damaged, or even the crystalline character of the wire is destroyed. Therefore, it is of great importance that the nanowire of which the interface to the substrate has to be studied is positioned in the centre of the membrane. To achieve this, the membrane is inspected directly in the FIB microscope from the 'front' and 'back' side by tilting it 45° (see fig. 1C). Hence, the exact locations of the, in this case 50 nm thick GaP, nanowires are visible. These regions are thinned further from the side where the wire is not yet visible. Once the membrane has a thickness of 100-200 nm it is transported to the TEM for a first inspection. By using HAADF (High Angle Annular Dark Field) imaging a direct link between the FIB front- and back-side images and the TEM cross-section image is obtained (see fig. 2A). Wires that need additional thinning can now be located. A final membrane thickness of 50-100 nm is achieved by sputtering with a beam current of 50-100 pA. Further improvement of the membrane quality can be achieved by low energy sputtering (e.g. by means of the 'Sidewinder' column (FEI)). When the membrane has reached its final thickness of 50-100 nm, high-resolution TEM imaging is possible of the interface between the GaP nanowire and the silicon substrate (fig. 2B and C). It is clear that the crystal lattice continues from the substrate into the wire, demonstrating the epitaxial growth. No lattice defects are present in the interface region. This implies that the 0.36% lattice mismatch between the GaP and the Si is accommodated solely by elastic deformation of the wire lattice [3]. It can be concluded that the quality of the interface shown here could perform electrically well.

In conclusion, combining FIB sample preparation with HAADF STEM imaging provided useful samples containing the interfaces of vertically grown nanowires on Si-substrates. The samples obtained could be studied using high-resolution TEM.

Fig. 1. A. Si-substrate with oxide encapsulated GaP nanowires as viewed from the top in the FIB. The region of interest is covered with Pt for protection (see dashed rectangle). B. membrane containing the nanowire of interest ready to be mounted on a TEM specimen grid. C. membrane containing the nanowire of interest as viewed from one side in the FIB.

Fig. 2. A. membrane containing a GaP nanowire(s) of interest as viewed in cross-section in the TEM using HAADF-STEM imaging. B. overview TEM image displaying the 'foot' of the wire. C. atomic resolution TEM image displaying a detail of the 'foot' of the wire.

## References

- [1] E.P.A.M. Bakkers et.al., Nature Materials 3 (2004) 769

- [2] S.M. Schwarz et.al., Microsc. Microanal. 9 (Suppl 2) (2003) 116

- [3] T. Martensson et.al., Nanoletters 4 (10) (2004) 1987