## A Versatile Common Platform for Quantum Transport Measurements in Fluidic, Cryogenic, and In Situ Electron Microscopy Environments

Jacob L. Swett<sup>1\*</sup>, Ivan I. Kravchenko<sup>2</sup>, O. E. Dyck<sup>2</sup>, S. Jesse<sup>2</sup>, and J. A. Mol<sup>1,3</sup>

- 1. Department of Materials, University of Oxford, Oxford, United Kingdom

- 2. Center for Nanophase Materials Sciences, Oak Ridge National Laboratory, Oak Ridge, United States of America

- 3. School of Physics and Astronomy, Queen Mary University of London, London, United Kingdom

- \* Corresponding author: jacob.swett@materials.ox.ac.uk

In Situ Transmission Electron Microscope (TEM) fabrication has made many advances recently, ranging from nanopore fabrication[1], to modification of 2D materials[2], to atomically precise manipulation[3], providing exciting opportunities for novel quantum architectures to be realized. However, to exploit the potential of these devices, measurements and characterization should ideally be possible *in situ* and also in the environment of the ultimate application, which can range from cryogenic temperatures for quantum computing[4] to liquid devices for quantum biosensors[5]. Here we present wafer-scale fabrication and validation of a common multi-functional extremely low-noise chip platform capable of *in situ* TEM characterization and fabrication, microfluidic experiments, and cryogenic and scanning probe measurements.

A key aspect to the success of the platform is the modular design allowing the chips to be interchangeable between applications as diverse as DNA sequencing devices, nanoscale heat transport experiments, and in situ fabrication of devices via TEM. We will briefly cover some of these projects and their results to date. With a particular focus on TEM fabricated quantum biosensors based on graphene quantum dots and *in situ* characterization of transport in suspended 2D materials.

The devices which each contain a single suspended low-stress silicon nitride window with or without apertures have eight contact pads allowing for a number of device to be biased simultaneously *in situ*. To enable sub-nanoampere level current measurements, thermal oxide is grown below the silicon nitride to reduce capacitive coupling of the electrodes to the substrate. Likewise, dielectric materials are utilized on top of the electrodes to reduce parasitic faradaic currents when in liquid environments and reduce capacitive coupling to conductive solutions.

Additionally, we will briefly cover the associated platforms enabling the various measurements, including *in situ* biasing holders and associated electronics, a biasing fluidic cell capable of simultaneously flowing fluid through the chips while measuring nanoampere-scale currents on the plane of the chip, and biasing devices for applications ranging from scanning probe measurements to cryogenic experiments. Finally, progress towards a new photonic architecture integrating on-chip wave guides will briefly be discussed.

- [1] Ivanov, A. P., et al. DNA tunneling detector embedded in a nanopore. Nano Lett **11.1**, (2010).

- [2] Heerema, S. J., et al. Probing DNA translocations with inplane current signals in a graphene nanoribbon with a nanopore. ACS Nano **12.3**, (2018).

- [3] Dyck, O. E., et al. Building structures atom by atom via electron beam manipulation. Small, **14.28** (2018).

- [4] Puczkarski, P., et al. Graphene nanoelectrodes for biomolecular sensing. J. Mater. Res. 32, (2017).

- [5] Gehring, P., et al. Quantum interference in graphene nanoconstrictions. Nano Lett, **16.7**, (2016).

- [6] The authors thank Scott Retterer, Kevin Lester, Dayrl Briggs, Bernadeta Srijanto, and James Yates for their assistance with aspects of the fabrication and design.

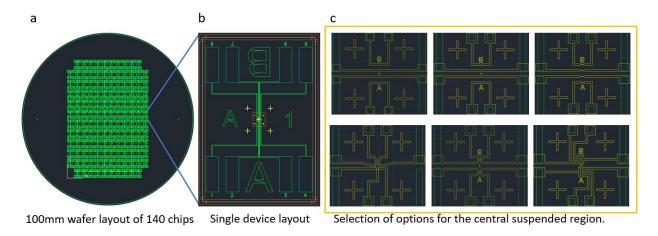

**Figure 1.** Figure 1: CAD renderings of a) the layout of a single 100mm wafer, b) a single 4.0 x 5.8mm chip showing the various layers, and c) a selection of some of the  $100 \times 100 \mu m$  interchangeable central regions for six different applications.

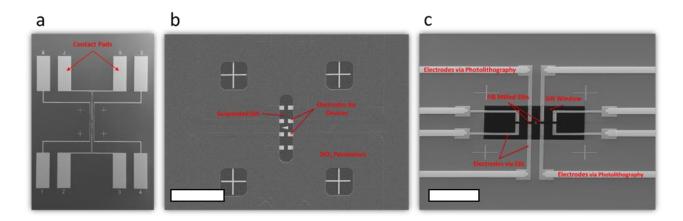

**Figure 2.** Figure 2: Scanning electron micrographs of a) a single 4.0 x 5.8mm chip, b) the central electron-transparent region of a chip with dielectric passivation, and c) the central electron transparent region of a chip without passivation showing the different layers. Scale bars are 20µm.